ouvir o artigo

A Revolução das Cidades de Silício: Entenda o Empilhamento 3D da TSMC

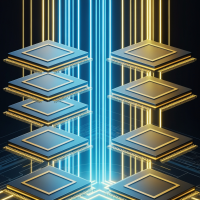

Imagine que você mora em uma cidade que não para de crescer. Tradicionalmente, para acomodar mais pessoas, a cidade se espalharia horizontalmente, ocupando quilômetros de terreno. O problema é que, quanto mais longe as casas ficam umas das outras, mais tempo as pessoas levam para se deslocar. No mundo dos computadores, estamos vivendo algo parecido. Os chips tradicionais estão ficando grandes demais e a comunicação entre seus componentes está ficando lenta. A solução da TSMC, a maior fabricante de semicondutores do mundo, é simples e genial: em vez de construir cidades planas, eles vão construir arranha-céus. Estamos falando do empilhamento vertical de chips.

Essa tecnologia é conhecida como SoIC (System on Integrated Chips). Ela permite que diferentes partes de um processador sejam colocadas umas sobre as outras, conectadas de forma tão íntima que parecem um único bloco de silício. Recentemente, a TSMC revelou um roteiro ambicioso que mostra como essa tecnologia vai evoluir nos próximos anos, prometendo mudar completamente o que entendemos por performance em hardware.

O que torna o SoIC tão especial?

Para entender o salto tecnológico, precisamos falar sobre como os componentes se conectam. Normalmente, usamos pequenas esferas de solda para ligar as partes de um chip. O SoIC descarta isso e utiliza o Hybrid Bonding (ligação híbrida). Nesse processo, o cobre de um chip toca o cobre do outro diretamente, sem solda no meio. Isso reduz drasticamente a distância que os dados precisam percorrer.

Atualmente, a TSMC trabalha com uma medida chamada “pitch”, que é a distância entre essas conexões microscópicas. Hoje, estamos na casa dos 6 micra. O novo plano da empresa prevê reduzir essa distância para 4,5 micra em 2027 e chegar a impressionantes 3 micra até 2029. Para você ter uma ideia, um fio de cabelo humano tem cerca de 70 micra de espessura. Estamos falando de uma precisão cirúrgica em escala atômica que permite colocar muito mais “estradas” de dados no mesmo espaço.

O Roadmap: O caminho até 2029

A evolução dessa tecnologia não acontece da noite para o dia. A TSMC dividiu esse progresso em etapas claras que acompanham a evolução das litografias, como o processo de 2 nanômetros (N2) e o futuro A16. Veja como essa linha do tempo se organiza:

- 2024-2025: Consolidação do SoIC com pitches de 6 micra, focado em computação de alto desempenho.

- 2026-2027: Introdução do SoIC com 4,5 micra, coincidindo com a chegada dos chips de 2nm de próxima geração.

- 2028-2029: Atingir o patamar de 3 micra, permitindo uma densidade de interconexão nunca antes vista na história da informática.

Essa progressão é fundamental porque, à medida que os transistores individuais param de encolher na velocidade que gostaríamos, a saída para continuar aumentando o poder de processamento é melhorar a forma como os componentes conversam entre si. O empilhamento 3D é, essencialmente, a cura para o gargalo de comunicação interna do hardware.

O Exemplo Real: O Processador MONAKA da Fujitsu

Não pense que isso é apenas teoria para o futuro distante. Um exemplo prático e fascinante é o processador MONAKA, da Fujitsu. Este chip será um dos primeiros a utilizar a técnica SoIC-X, que é o empilhamento “face-to-face” (frente a frente). Nele, as camadas lógicas do chip são viradas uma contra a outra, permitindo que a troca de informações ocorra com latência quase zero.

O MONAKA usará a litografia de 2nm da TSMC e contará com dezenas de núcleos de processamento cercados por memórias de alta velocidade. Esse design só é possível graças ao SoIC, que permite que o processador consuma muito menos energia enquanto entrega uma largura de banda imensa. É o tipo de tecnologia que hoje equipa supercomputadores, mas que em breve ditará o ritmo dos nossos PCs domésticos e dispositivos móveis.

As Diferentes Formas de Empilhar

A TSMC não está presa a apenas um método. Eles desenvolveram variações para diferentes necessidades. Além do SoIC-X (frente a frente), existe o SoIC-P (frente para trás). No SoIC-P, os chips são empilhados como pratos em uma prateleira, o que é mais simples de fabricar e ideal para memórias e sensores. Já o SoIC-X é o rei da performance, permitindo que o calor seja dissipado de forma mais eficiente em algumas configurações, embora o gerenciamento térmico continue sendo o maior desafio dessa engenharia vertical.

O Desafio do Calor e a Eficiência Energética

Colocar um chip em cima do outro cria um problema óbvio: o chip de baixo fica “preso” e o calor tem dificuldade de sair. A TSMC está resolvendo isso com materiais avançados e novas estruturas de resfriamento. A grande vantagem é que, como a comunicação entre os chips exige menos energia elétrica para mover os dados (já que as distâncias são minúsculas), o sistema como um todo acaba gerando menos calor por operação realizada do que um chip plano equivalente.

Por que você deve se importar com isso?

Você pode estar se perguntando: “O que eu ganho com chips empilhados?”. A resposta curta é: eficiência e longevidade. Com o empilhamento 3D, poderemos ter notebooks muito mais finos com poder de processamento de desktops, ou smartphones que executam inteligência artificial complexa localmente sem descarregar a bateria em minutos.

A Oficina dos Bits acompanha essas mudanças de perto porque elas definem o que você terá na sua mesa daqui a três ou quatro anos. O fim da era dos chips “planos” marca o início de uma computação muito mais integrada, onde a barreira entre processador, memória e placa de vídeo começa a desaparecer em favor de um único e poderoso bloco vertical de tecnologia pura.